# The Institution of Electronics ETE Journal of Rese

**IETE** Journal of Research

ISSN: (Print) (Online) Journal homepage: https://www.tandfonline.com/loi/tijr20

### Ultra-Low Power 8-Transistor Modified Gate **Diffusion Input Carbon Nano-Tube Field Effect Transistor Full Adder**

Priyanka Tyagi, Sanjay Kumar Singh & Piyush Dua

To cite this article: Priyanka Tyagi, Sanjay Kumar Singh & Piyush Dua (2023) Ultra-Low Power 8-Transistor Modified Gate Diffusion Input Carbon Nano-Tube Field Effect Transistor Full Adder, IETE Journal of Research, 69:8, 5518-5531, DOI: 10.1080/03772063.2021.1962746

To link to this article: https://doi.org/10.1080/03772063.2021.1962746

Published online: 19 Aug 2021.

Submit your article to this journal 🕝

View related articles

View Crossmark data 🗹

Citing articles: 2 View citing articles 🗹

### Ultra-Low Power 8-Transistor Modified Gate Diffusion Input Carbon Nano-Tube Field Effect Transistor Full Adder

### Priyanka Tyagi 1, Sanjay Kumar Singh<sup>2</sup> and Piyush Dua 13

<sup>1</sup>Research Scholar, Department of Electronic and Communication, AKTU, Lucknow, UP, India; <sup>2</sup>Department of ECE, ABES Engineering College, Ghaziabad, UP, India; <sup>3</sup>Department of Engineering, University of Technology and Applied Sciences, Suhar, Sultanate of Oman

#### ABSTRACT

An ultra-low power 8-Transistor Modified Gate Diffusion Input (MGDI) Carbon Nano Tube Field Effect Transistor (CNTFET) Full Adder (FA) has been presented in this paper. The proposed 8-T MGDI CNT-FET Full Adder outperforms other adders in terms of Power Consumption, Propagation Delay and the PDP at different levels of Power Supply and Temperatures. The power consumption of the proposed 10 nm CNTFET 8-T MGDI Full Adder at 27°C is 1.96 nW. The proposed CNTFET FA exhibits 60.32% improvement in Power Consumption when compared to the existing 10 nm FINFET 8-T MGDI Full Adder. The propagation Delay of the proposed FA is 42.16 ps and an improvement of 57.68% is noticed over the existing FA. The Power Delay Product of the proposed 10 nm CNTFET 8-T MGDI FA is 82.63  $\times$  10<sup>-21</sup> Jules, whereas the PDP of the 10 nm FINFET 8-T MGDI FA is 492.07  $\times$  10<sup>-21</sup> Jules. The PDP of the proposed 10 nm CNTFET 8-T MGDI FA.

#### **KEYWORDS** CNTFET; FINFET; Full Adder;

CNTFET; FINFET; Full Adder, MGDI; Ultra-low power; 8-Transistor Full Adder

### **1. INTRODUCTION**

In the modern digital electronics the 1-bit full adder is a basic block for arithmetic units, memory units and different logical operations. The full adder cell is deployed in other circuits such as multipliers and different kinds of adders, such as RippleCarry Adder (RCA), Carry Save Adder (CSA), *etc.* The above-mentioned adders are used in various data path elements to perform different arithmetic operations. Hence, a novel fast, low-power, and low area 8- T MGDI full adder cell has been proposed using10 nm CNTFET in this paper.

The regular Metal–Oxide Semiconductor Field Effect Transistors (MOSFETs) come across serious difficulties at the nano-scale region, such as the huge leakage current, short-channel effects, process-corner variations, *etc* [1,2]. Consequently, a few innovative technologies had emerged for nano-electronics in the recent years. Carbon Nano Tube Field Effect Transistor (CNTFET) is the guaranteed technology instead of MOSFET devices. CNTFET offers great flexibility to design low-power and high-performance circuits and CNTFET has very low offcurrent [3]. The performance and efficiency of the proposed CNTFET FA has been analyzed across all Process-Voltage-Temperature (PVT) corners. Mostly single-wall carbon-nanotubes (SWCNTs) are used as channels in CNTFET. Depending upon the chirality vector CNTs can be work as semiconductors, metals or conductors [4]. High Speed and Low Power CNTFET approximate FA Cell for Image Processing Application has been implemented [5].

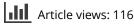

Carbon nanotubes (CNTs) are most promising onesin today's electronic world. CNT has the 1D quasistructure. The unique properties of the CNTs led their use in nano-applications. The properties of CNTs are determined by their fabrication process [6]. CNTs, mainly SWCNTs, are the up-growing material for the electronic field. SWCNTs are going to take the place of the silicon in the coming years. CNTFETs are going to replace the silicon-based transistors [7]. The main advantage of the CNT is that it reduces the amount of material used in the fabrication process. The conventional silicon transistor requires the bulk of silicon. CNT reduces the amount of the material used for the fabrication of the transistors [8]. The properties such as high mobility of the carrier, low capacitance and the nanometer channel length promote the use of CNTs for ultra-high speed applications [9]. CNFETs are used to design low power and high performance circuits [10,11]. CMOS devices have large leakage currents and short-channel effects [10-12]. SWCNT can act as a conductor (metal) and as a semiconductor as well [11,12]. Figure 1 shows the gate-all-around structure of CNTFET.

Figure 1: 3D structure of the CNTFET model

The remainder of the research article is structured as follows. Related research work on CNTFET-FA has been discussed in Section 2. Design of the proposed CNTFET-FA cell has been offered in Section 3. Simulation outcomes have been discussed in Section 4. Finally, Section 5 concludes the paper.

### 2. RELATED RESEARCH WORK

Different implementations of full-adder cells are available in the literature [12–20]. Few full adders were employed with MOSFETs and CNTFETs. The complementarypass-transistor logic FA [14] was implemented using a 32-transistor. The CNTFET-FA implemented by the majority function is presented in [15]. Complementary-CMOS (C-CMOS) FA [16] using 28-transistors was implemented.

The multi-output-dynamic FA [17] using 21-transistors was proposed. Transmission-gates [18] using 20-transistors were presented. A high-speed capacitor-inverterbased CNTFET-FA is presented [19]. Energy-efficient CNTFET-FA [20] based on majority function, 8-transistors and 5-capacitors is offered. 14-transistor CNTFET-FA [21] was implemented. A dynamic-CNTFET-FA cell [22], 8 T MGDI CMOS Full Adder cell [23] and 8 T MGDI FINFET Full Adder [24] were implemented.

High-Efficient Full Adder Circuit was implemented by Seyedehsomayeh [25]. CNTFET-based Low Power Ternary Full Adder was discussed by F. Jafarzadehpour *et al.* [26]. CNTFET-based Quaternary Full Adder was implemented by Krishna Chaitanya *et al.* [27]. Carbon nanotube FET-based multi-digit adder was implemented to optimize the parameter such as power and delay by B. Srinivasu *et al.* [28]. A CNTFET Ternary Full adder for Carry Generation Circuit to improve the performance of the design was implemented by Subhendu Kumar Sahoo *et al.* [29].

A full adder cell is designed using a XOR–XNOR gate and a multiplexer circuit [30]. The design has the 23 transistors. The sum was designed by the transmission gate technique and the carry output design was implemented by the GDI technique. This adder is used to implement the 4:2 compressors.

The proposed full adder is implemented using 20 transistors [31]. The high-performance design is applicable for different carry adder formats. The 14T high-speed GDI full adder is implemented with two different strategies [32]. A power-efficient 10 T full adder was designed using majority of NOT function [33].

### 3. PROPOSED RESEARCH WORK

The CNTFET has very less effect of temperature on the threshold voltage, but the threshold voltage of the MOSFET decreases drastically with temperature. So, the leakage power in MOSFET circuits will be huge at high temperature and the leakage power increases exponentially with the rise in temperature. But, the impact of the temperature on the leakage power of the CNTFET is very minimal and it increases gradually with the rise in temperature. Hence the CNTFET circuit exhibits excellent Power, Performance and Area (PPA) optimization.

An ultra-low power 8-Transistor Modified-Gate-Diffusion-Input (MGDI) Carbon-Nano-Tube-Field-Effect-Transistor (CNTFET) Full Adder (FA) has been presented in this paper. The proposed CNTFET Full Adder has been implemented using the 10 nm CNTFET model and "10" Carbon Nano Tubes are used as channels under the gate to conduct the current from the source to drain. The performance metrics of the proposed 8-T MGDI CNTFET FA have been compared with those of the existing 8-T MGDI FINFET FA.

The proposed 8-T MGDI CNTFET FA consumes very less power because of the proposed structure and the Full Adder is operated with 0.5 V as the power supply. Power supply voltage is 0.5 V because the threshold-voltage of CNTFET is in terms of microvolts. Hence the switching speed of the proposed circuit is not affected. Moreover, the low power supply provides very good optimization in the power consumption of the proposed circuit because of the negligible amount of parasitic capacitance of the proposed CNTFET models. Hence the proposed 8-T MGDI CNTFET FA outperforms well by means of the

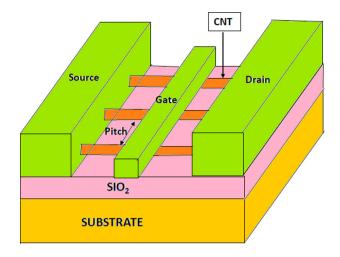

Figure 2: Schematic diagram of 8-T MGDI FINFET full adder [24]

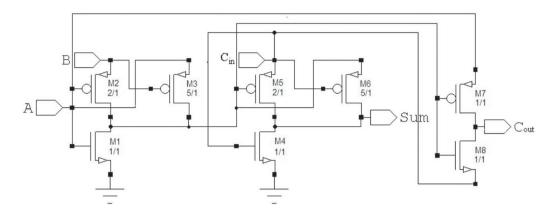

Figure 3: Schematic diagram of the proposed 8 T MGDI CNTFET FA

energy requirement, delay and PDP. So, the overall performance of the proposed FA is excellent when compared with the existing Full Adder designs.

Schematic diagram of the existing 8-T MGDI FINFET-FA has been displayed in Figure 2.

The existing 8-T MGDI FINFET FA circuit was implemented using a 10 nm FINFET library and the supplyvoltage is 0.7 V. Schematic of the proposed 8-T MGDI CNTFET FA has been shown in Figure 3. The proposed 8-T MGDI CNTFET FA schematic diagram has been drawn using 10 nm N-CNTFET and P-CNTFET models in Cadence Schematic Composer Tool in Virtuoso Analog Design Environment.

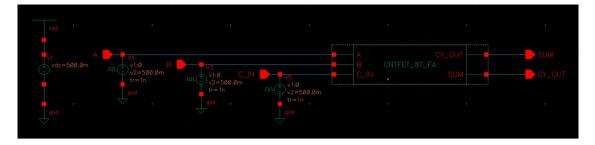

The Test Bench of the proposed CNTFET-FA is displayed in Figure 4. The power supply voltage is 0.5 V. Pulse signals are given to the input terminals "A", "B", "C\_IN" to generate all possible "8" combinations to the adder. The voltage level of the inputs is also 0.5 V. Transient analysis in Cadence is used to analyze the performance metrics of

| Table | 1: Truth | table of | a full | adder |

|-------|----------|----------|--------|-------|

|-------|----------|----------|--------|-------|

| Input-A | Input-B | Input-C_IN | SUM | CY_OUT |

|---------|---------|------------|-----|--------|

| 0       | 0       | 0          | 0   | 0      |

| 0       | 0       | 1          | 1   | 0      |

| 0       | 1       | 0          | 1   | 0      |

| 0       | 1       | 1          | 0   | 1      |

| 1       | 0       | 0          | 1   | 0      |

| 1       | 0       | 1          | 0   | 1      |

| 1       | 1       | 0          | 0   | 1      |

| 1       | 1       | 1          | 1   | 1      |

|         |         |            |     |        |

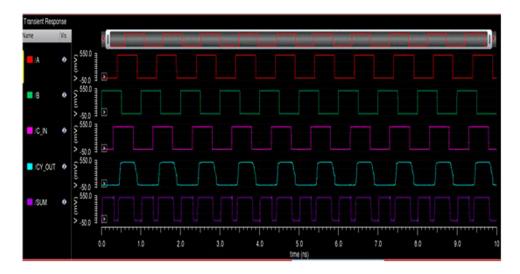

the proposed 8-T MGDI CNTFET-FA. The Truth-table of the FA is listed in Table 1. Input out waveforms of the proposed Full Adder is shown in Figure 5.

### 4. SIMULATION RESULTS AND DISCUSSION

The proposed 8-T MGDI CNTFET FA has been implemented using 10 nm N-CNTFET and P-CNTFET models in the Cadence Schematic Composer Tool in Virtuoso Analog Design Environment.

Figure 4: Test bench of the proposed 8 T CNTFET FA

Figure 5: Input–output waveform of the proposed 8-T MGDI CNTFET

| Table 2: Simulation | parameters of the |

|---------------------|-------------------|

| proposed circuit    |                   |

| Parameters              | Values/Description |

|-------------------------|--------------------|

| Technology Node         | 10 nm CNTFET       |

| Length of the CNT       | 10 nm              |

| Width of the CNT        | 1 μm               |

| No of Carbon Nano-Tubes | 10                 |

| Power Supply            | 0.5 V              |

| Range of Power Supply   | 0.4 to 1.0 V       |

| Simulation Temperature  | 27°C               |

| Range of Temperatures   | -25°C to 125°C     |

| Analysis                | Transient          |

The length of the Carbon Nano Tube channel is 10 nm and "10" Carbon Nano Tubes are under the gate to conduct the current from the Source terminal to the Drain terminal. The simulation parameters have been listed in Table 2.

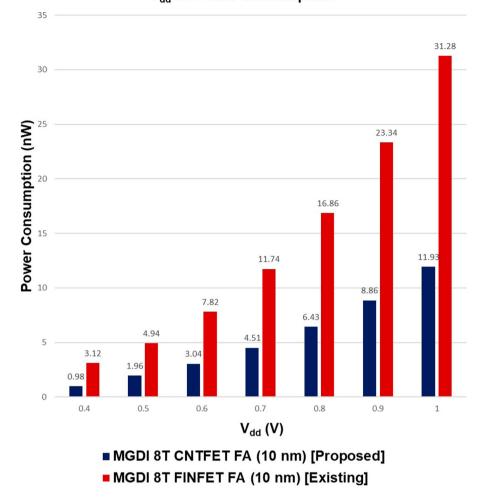

Supply Voltage is 0.5 V and the simulation temperature is 27°C. Transient analysis in Cadence is used to analyze the performance metrics of the proposed 8-T MGDI CNTFET FA. The performance metrics, such as Power Consumption, Propagation Delay and the Power Delay Product, are measured and analyzed. The impact of the variation in the power supply on power consumption of

### Table 3: Power supply variations vs. power consumption @ 27°C

| Power<br>Supply<br>V <sub>dd</sub> (V) | 8 T MGDI CNTFET FA<br>(10 nm) [Proposed]<br>Power (nW) | 8 T MGDI FINFET FA<br>(10 nm) [20]<br>Power (nW) |

|----------------------------------------|--------------------------------------------------------|--------------------------------------------------|

| 0.4                                    | 0.98                                                   | 3.12                                             |

| 0.5                                    | 1.96                                                   | 4.94                                             |

| 0.6                                    | 3.04                                                   | 7.82                                             |

| 0.7                                    | 4.51                                                   | 11.74                                            |

| 0.8                                    | 6.43                                                   | 16.86                                            |

| 0.9                                    | 8.86                                                   | 23.34                                            |

| 1.0                                    | 11.93                                                  | 31.28                                            |

|                                        |                                                        |                                                  |

the proposed 8-T MGDI CNTFET FA and the existing 8-T MGDI FINFET FA is listed out in Table 3.

The power supply is varied from 0.4 V up to 1.0 V in steps of 0.1 V and the corresponding power consumption at 27 °C has been listed. The proposed CNTFET FA exhibits 60.32% improvement in Power Consumption when compared to the existing 10 nm FINFET 8-T MGDI Full Adder.

The graphical representation of the effect of power supply variation on the power consumption is depicted in Figure 6. The impact of the variation in the power supply

### V<sub>dd</sub> Vs Power Consumption

Figure 6: Effect of power supply variations on power consumption

| delay @ 27°C        |                        |                             |  |  |

|---------------------|------------------------|-----------------------------|--|--|

| Power               | 8 T MGDI CNTFET FA     | 8 T MGDI FINFET FA          |  |  |

| Supply              | (10 nm) [Proposed]     | (10 nm) [ <mark>20</mark> ] |  |  |

| V <sub>dd</sub> (V) | Propagation Delay (ps) | Propagation Delay (ps)      |  |  |

| 0.4                 | 49.57                  | 372.91                      |  |  |

| 0.5                 | 82.63                  | 492.07                      |  |  |

| 0.6                 | 102.51                 | 623.09                      |  |  |

| 0.7                 | 114.05                 | 701.58                      |  |  |

| 0.8                 | 108.41                 | 671.71                      |  |  |

| 0.9                 | 78.23                  | 464.93                      |  |  |

| 1.0                 | 13.01                  | 256.18                      |  |  |

Table 4: Power supply variations vs. propagation

delay @ 27°C

on propagation delay of the proposed 8-T MGDI CNT-FET FA and the existing 8-T MGDI FINFET FA are listed in Table 4.

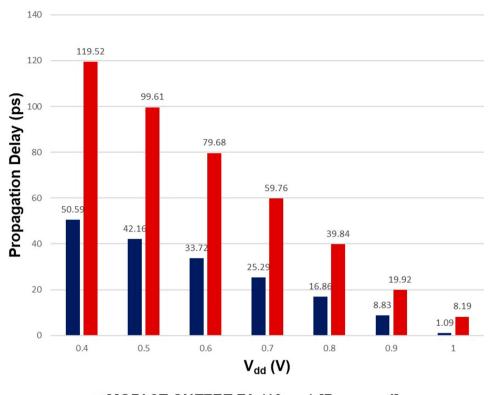

The power supply voltage is varied from 0.4 V up to 1.0 V in steps of 0.1 V and the corresponding propagation delay at 27°C has been listed. The Propagation Delay of the proposed FA is 42.16 ps and an improvement of 57.68% has been noticed over the existing FA.

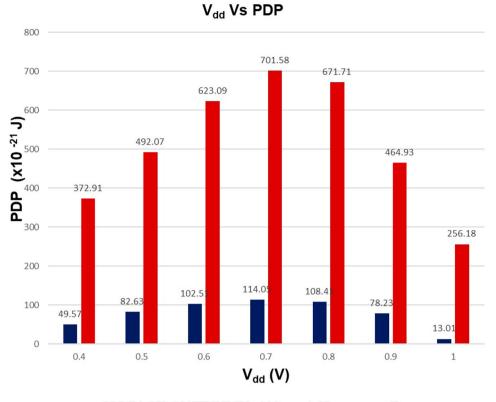

The graphical representation of the effect of power supply variation on the propagation delay is depicted in Figure 7. The impact of the variation in the power supply on PDP of the suggested 8-T MGDI CNTFET-FA and the existing 8-T MGDI FINFET FA is listed in Table 5.

Power supply voltage is varied from 0.4 V up to 1.0 V in steps of 0.1 V and the corresponding power delay product at 27°C has been listed. The PDP of the proposed 10 nm CNTFET 8-T MGDI Full Adder is  $82.63 \times 10^{-21}$  Jules, whereas the PDP of the 10 nm FINFET 8-T MGDI FA is 492.07  $\times 10^{-21}$  Jules. The Power Delay Product of the proposed 10 nm CNTFET 8-T MGDI Full Adder exhibits 83.21% improvement when compared to the 10 nm FINFET 8-T MGDI FA. The graphical representation of the effect of power supply variation on the PDP is shown in Figure 8.

The impact of the variation in the simulation temperature on power consumption of the proposed 8-T MGDI V<sub>dd</sub> Vs Delay

# MGDI 8T CNTFET FA (10 nm) [Proposed] MGDI 8T FINFET FA (10 nm) [Existing]

Figure 7: Effect of power supply variations on propagation delay

| Power               | 8 T MGDI CNTFET FA             | 8 T MGDI FINFET FA             |

|---------------------|--------------------------------|--------------------------------|

| Supply              | (10 nm) [Proposed]             | (10 nm) [ <mark>20</mark> ]    |

| V <sub>dd</sub> (V) | PDP (x10 <sup>-21</sup> Jules) | PDP (x10 <sup>-21</sup> Jules) |

| 0.4                 | 49.57                          | 372.91                         |

| 0.5                 | 82.63                          | 492.07                         |

| 0.6                 | 102.51                         | 623.09                         |

| 0.7                 | 114.05                         | 701.58                         |

| 0.8                 | 108.41                         | 671.71                         |

| 0.9                 | 78.23                          | 464.93                         |

| 1.0                 | 13.01                          | 256.18                         |

### CNTFET FA and the existing 8-T MGDI FINFET FA is given in Table 6.

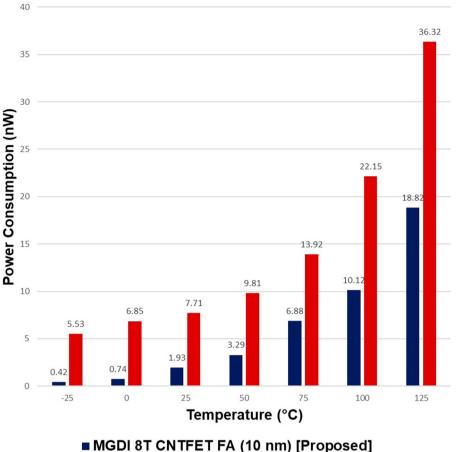

The simulation temperature is varied from  $-25^{\circ}$ C up to  $+125^{\circ}$ C in steps of  $+25^{\circ}$ C and the corresponding power consumption at the power supply voltage of 0.5 V has been given.

The power consumption of the proposed 8-T MGDI CNTFET FA at 27°C is 1.93 nW, whereas the power consumption of the 8-T MGDI FINFET FA at 27°C is 7.70 nW. The proposed 8-T MGDI CNTFET FA exhibits a

| Table 6: Effect of te | emperature | on | power |

|-----------------------|------------|----|-------|

| consumption @ Vdd     | = 0.5 V    |    |       |

|             | -                     |                       |

|-------------|-----------------------|-----------------------|

|             | 8 T MGDI<br>CNTFET FA | 8 T MGDI<br>FINFET FA |

| Temperature | (10 nm) [Proposed]    | (10 nm) [20]          |

| (°C)        | Power (nW)            | Power (nW)            |

| -25         | 0.42                  | 5.53                  |

| 0           | 0.74                  | 6.85                  |

| 25          | 1.93                  | 7.71                  |

| 50          | 3.29                  | 9.81                  |

| 75          | 6.88                  | 13.92                 |

| 100         | 10.12                 | 22.15                 |

| 125         | 18.82                 | 36.32                 |

|             |                       |                       |

gradual increment in Power Consumption as the temperature increases, whereas 8-T MGDI FINFET FA Power Consumption increases drastically as the temperature increases and this is exhibited in Figure 9.

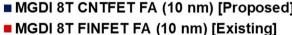

The impact of the variation in the simulation temperature on propagation delay of the proposed 8-T MGDI CNTFET FA and the existing 8-T MGDI FINFET FA is given in Table 7. The simulation temperature is varied from  $-25^{\circ}$ C up to  $+125^{\circ}$ C in steps of  $+25^{\circ}$ C and

# MGDI 8T CNTFET FA (10 nm) [Proposed] MGDI 8T FINFET FA (10 nm) [Existing]

Figure 8: Effect of power supply variations on power delay product

.

| Table 7: Effect of temperature on propagation delay |                        |                             |  |

|-----------------------------------------------------|------------------------|-----------------------------|--|

|                                                     | 8 T MGDI               | 8 T MGDI                    |  |

|                                                     | CNTFET FA              | FINFET FA                   |  |

| Temperature                                         | (10 nm) [Proposed]     | (10 nm) [ <mark>20</mark> ] |  |

| (°C)                                                | Propagation Delay (ps) | Propagation Delay (ps)      |  |

| -25                                                 | 21.76                  | 47.17                       |  |

| 0                                                   | 32.19                  | 76.21                       |  |

| 25                                                  | 43.94                  | 102.43                      |  |

| 50                                                  | 53.59                  | 128.65                      |  |

| 75                                                  | 67.95                  | 161.41                      |  |

| 100                                                 | 91.36                  | 204.61                      |  |

| 125                                                 | 133.09                 | 264.06                      |  |

the corresponding propagation delay at the power supply voltage of 0.5 V has been given.

The propagation delay of the proposed 8-T MGDI CNT-FET FA at 27°C is 42.16 ps, whereas the power consumption of the 8-T MGDI FINFET FA at 27°C is 99.61 ps. The proposed 8-T MGDI CNTFET FA exhibits a gradual decrement in propagation delay as the temperature increases, whereas 8-T MGDI FINFET FA propagation delay decreases drastically as the temperature increases and this is shown in Figure 10.

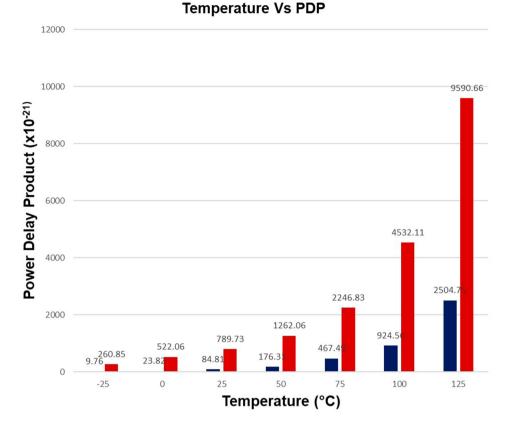

The impact of the variation in the simulation temperature on PDP of the proposed 8-T MGDI CNTFET FA and the existing 8-T MGDI FINFET FA is displayed in Table 8. The simulation temperature is varied from  $-25^{\circ}$ C up to  $+125^{\circ}$ C in steps of  $+25^{\circ}$ C and the corresponding PDP at the power supply voltage of 0.5 V has been given. The PDP of the proposed 8-T MGDI CNTFET FA at 27°C is 84.81 × 10<sup>-21</sup> J, whereas the PDP of the 8-T MGDI FINFET FA at 27°C is 789.73 × 10<sup>-21</sup> J.

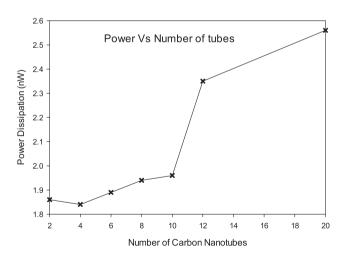

### 4.1 Number of CNT and Diameter Variation

The current characteristics of the CNTFET depend upon the number of the CNTs under the channel. The current flow in the channel is due to the mobile charge carriers in the nanotube channel. The current is directly proportional to the number of tubes. The variation in the CNT number affects the power dissipation and delay of the circuit. For the proposed circuit, the number of tubes is 10. The simulation result variation for power dissipation is done for 2–20 nanotubes.. The simulation variation is shown in Figure 12. The power dissipation of the proposed 8 T MGDI CNTFET FA is 1.96nW for the optimized number of tubes. The simulation shows the gradual increment in the power consumption as the number of tubes increased.

### **Temperature Vs Power Consumption**

Figure 9: Effect of temperature on power consumption

Table 8: Effect of temperature on power delay product

|             | 8 T MGDI<br>CNTFET FA                       | 8 T MGDI<br>FINFET FA                       |

|-------------|---------------------------------------------|---------------------------------------------|

| Temperature | (10 nm) [Proposed]                          | (10 nm) [20]                                |

| (°C)        | PDP (x10 <sup><math>-21</math></sup> Jules) | PDP (x10 <sup><math>-21</math></sup> Jules) |

| -25         | 9.76                                        | 260.85                                      |

| 0           | 23.82                                       | 522.06                                      |

| 25          | 84.81                                       | 789.73                                      |

| 50          | 176.31                                      | 1262.06                                     |

| 75          | 467.49                                      | 2246.83                                     |

| 100         | 924.56                                      | 4532.11                                     |

| 125         | 2504.75                                     | 9590.66                                     |

|             |                                             |                                             |

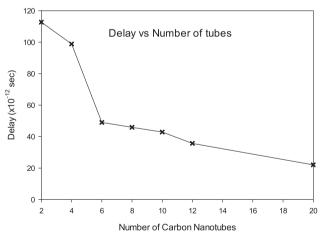

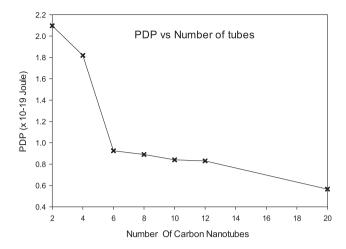

The propagation delay of the circuit also has an impact on the number of tubes. The variation in the delay with respect to the number of tubes is shown in Figure 13. The delay reduces as the number of tubes increases. The less propagation time will enhance the efficiency of the circuit. For the proposed circuit 8 T MGDI CNTFET FA has 42.16ps delay at 10 nanotubes. It has optimized the value of the propagation time to achieve better performance. The PDP has an effect of the delay and power dissipation. As the number of tubes increases the PDP will decreases. The PDP variation of the Proposed 8 T MGDI CNTFET FA depends upon the number of tubes shown in Figure 14. The PDP of the proposed design is  $82.63 \times 10^{-21}$  joule when the numbers of the tubes is 10 under the CNTFET gate terminal.

The performance of the circuit can be evaluated for different diameters of the CNTs. The diameter is the key component for the CNT performance. The performance of the CNTFET-based adder mostly depends upon the chirality of the CNT. The diameter of the carbon nanotubes depends on the chirality vector [33]. The diameter can be calculated by using the chirality parameter shown in Equation (1) [34].

$$D_{\rm CNT} = \frac{a\sqrt{n_1^2 + n_2^2 + n_1 n_2}}{\pi} \approx 0.0783 \sqrt{n_1^2 + n_2^2 + n_1 n_2}$$

(1)

### **Temperature Vs Propagation Delay**

$n_1$  and  $n_2$  are the chirality parameters. These parameters decide the type of the CNTs. The CNT is in metal type if  $n_1$  equals to  $n_2$ .

The CNT is a semiconductor if  $n_1$  is not equal to  $n_2$ . The threshold voltage of the carbon nanotube depends on the diameter of the CNT. The calculation of the threshold voltage using the diameter is shown in Equation (2).

$$V_{\rm th} \cong \frac{E_g}{2e} \cong \frac{\sqrt{3}aV\pi}{3eD_{\rm CNT}} \cong \frac{0.43}{D_{\rm CNT}}$$

(2)

where a = 2.49 Å is the atomic distance between two carbon atoms. V = 3.033 eV is the carbon  $\pi$ - $\pi$  bond energy, "e"is the electron unit charge. The current flow in the CNTFET depends upon the threshold voltage of the transistor. The threshold voltage is reducing with the increment in the diameter of the tube. For the CNTFET current flows in the channel are also affected by the diameter of the CNT. The diameter of the CNTs can be varied from 1 nm to 3 nm. The variations are shown for chirality

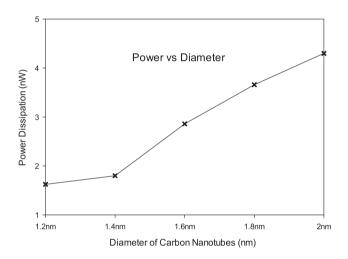

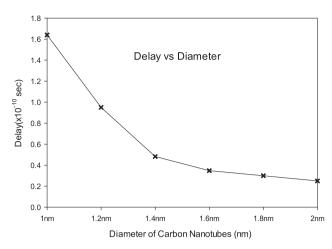

vectors (13,0), (16,0),(19,0), (21,0) and (23,0). The diameters for the given chirality are 1, 1.25, 1.48, 1.64 and 1.8 nm, respectively. The optimized diameter for the proposed design is 1.48 nm which has the chirality vectors (19,0). The variation in the power dissipation due to the diameter is shown in Figure 15. The power is related to the threshold voltage. As the diameter increases the threshold voltage decreases. The power increases gradually with the increment in the diameter. The efficient value of the power can be measured at 1.48 nm diameter tube. The effect of the diameter on the propagation delay is shown in Figure 16. The propagation time has a large impact on the diameter of the nanotubes. The proposed 8T MGDI CNTFET FA shows that the higher the nanotube diameter, the lesser the propagation delay.

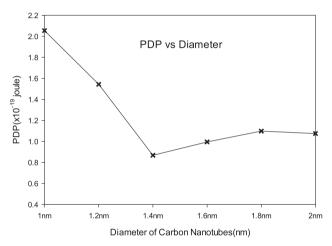

The variation in diameter also affects the power delay product. The PDP is the product of power dissipation and the delay. For the proposed design CNTFET-based design variation is shown in Figure 17.

# MGDI 8T CNTFET FA (10 nm) [Proposed] MGDI 8T FINFET FA (10 nm) [Existing]

Figure 11: Effect of temperature on power delay product

Figure 12: Effect of the number of CNTs on power dissipation

Figure 13: Effect of the number of CNTs on delay

The proposed 8-T MGDI CNTFET FA exhibits a gradual increment in PDP up to 0.7 V as the temperature increases and gradual increment in PDP after that, whereas 8-T MGDI FINFET FA PDP increases drastically up to 0.7 V as the temperature increases and decreases drastically after that and this is shown in Figure 11. The performance metrics of different CNTFET Full Adders have been compared in Table 9. The proposed 10 nm 8-T MGDI CNTFET FA outperforms by means of energy requirement, delay and PDP.

Figure 14: Effect of the number of CNTs on PDP

Figure 15: Effect of CNT diameter on power dissipation

SDTSPC logic-based Fin FET Full adder was implemented for high performance [35]. The main advantage of the SDTSPC logic is that it reduces the problem of charge sharing and noise fluctuation in dynamic logic circuits. The design was implemented by IG-FinFET. This technique was used to reduce the consumption of power and enhance the speed of the circuit. The power consumption of the FinFET full adder was 150.6nW and delay was  $196.57 \times 10^{-12}$  sec for the 0.5volt supply voltage. Over the advantages of the logic the implemented design has a large number of transistors. The implemented design has a large area and high power dissipation in comparison to the proposed MGDI full adder. The 10T GDI-based FinFET adder was proposed by Pavan et al. [36]. It showed the improvement in the performance in comparison to the CMOS design. The power dissipation of the design was 528.9 nW. The delay of sum and PDP was 32.89 psec and 17.35  $\times$   $10^{-18}$  joule for 45 nm node, respectively.

Figure 16: Effect of CNT diameter on delay

Figure 17: Effect of CNT diameter on PDP

Table 9: Comparison between the proposed designs and other CNTFET full adders

| Full<br>Adder         | Supply<br>Voltage<br>(Volts) | Number of<br>Transistors | Delay<br>(ps) | Power<br>(nW) | PDP<br>(x10 <sup>-19</sup> J) |

|-----------------------|------------------------------|--------------------------|---------------|---------------|-------------------------------|

| Design in<br>[30]     | 0.8                          | 23                       | 14134         | 1165          | 164650                        |

| Design in<br>[31]     | 0.5                          | 20                       | 58.8          | 266           | 157                           |

| Design in<br>[32]     | 0.8                          | 14                       | 6.39          | 733           | 47.15                         |

| Design in<br>[33]     | 0.5                          | 10                       | 1132          | 2.51          | 28.3                          |

| Design in<br>[24]     | 0.5                          | 8                        | 89.3          | 67.39         | 60.17                         |

| Proposed<br>CNTFET    |                              |                          |               |               |                               |

| (10 nm) Full<br>Adder | 0.5                          | 8                        | 42.16         | 1.96          | 0.8263                        |

### 5. CONCLUSIONS

An ultra-low power 8-Transistor MGDI CNTFET-FA has been presented in this paper. Various performance metrics, such as energy requirement, delay and PDP, have been analyzed with variation in the Power Supply voltage and variation in the Simulation Temperature. The proposed 8-T MGDI CNTFET Full Adder outperforms well by means of energy requirement, delay and PDP at different levels of Power Supply and Temperatures. The power consumption of the proposed 10 nm CNTFET 8-T MGDI Full Adder at 27°C is 1.96 nW. The proposed CNTFET FA exhibits 60.32% improvement in Power Consumption when compared to the existing 10 nm FIN-FET 8-T MGDI Full Adder. The propagation Delay of the proposed FA is 42.16 ps and an improvement of 57.68% has been noticed over the existing FA. The PDP of the proposed 10 nm CNTFET 8-T MGDI Full Adder is  $82.63 \times 10^{-21}$  Joules, whereas the PDP of the 10 nm FINFET 8-T MGDI FA is  $492.07 \times 10^{-21}$  Joules. The Power Delay Product of the proposed 10 nm CNTFET 8-T MGDI Full Adder exhibits 83.21% improvement when compared to the 10 nm FINFET 8-T MGDI FA.

### ACKNOWLEDGEMENT

The author PT is thankful to the officials of AKTU, Lucknow for their continuous support and motivation.

### ORCID

*Priyanka Tyagi* http://orcid.org/0000-0003-3770-9737 *Piyush Dua* http://orcid.org/0000-0002-5444-1384

### REFERENCES

- S. Lin, Y. B. Kim, and F. Lombardi, "A novel CNTFETbased ternary gate design," in *Proceedings of the IEEE 52nd International Midwest Symposium on Circuits and Systems*, Cancun, Mexico, 2009, pp. 435–438.

- Y. S. Mehrabani, and M. Eshghi, "High-speed, high-frequency and low-PDP, CNFET full adder cells," *J. Circuits Syst. Comput.*, Vol. 24, pp. 1–24, 2015. DOI:10.1142/S021-8126615501303

- A. Rahman, L. Guo, S. Datta, and M. S. Lundstrom, "Theory of ballistic nanotransistors," *IEEE Trans. Electron Devices*, Vol. 50, pp. 1853–1864, 2003. DOI:10.1109/TED. 2003.815366

- A. Raychowdhury, and K. Roy, "Carbon nanotube electronics: design of high-performance and low-power digital circuits," *IEEE Trans. Circuits Syst.*, Vol. 54, pp. 2391–2401, 2001. DOI:10.1109/TCSI.2007.907799

- Y. S. Mehrabani, R. F. Mirzaee, Z. Zareei, and S. M. Daryabari, "A novel high-speed, low-power CNTFET-based inexact full adder cell for image processing application of motion detector," *J. Circuits Syst. Comput.*, Vol. 26, pp. 1–15, 2016.

- N. R. Shanmugam, and S. Prasad, "Characteristics of Carbon Nanotubes for Nanoelectronic Device Applications," in *Nanopackaging*, Cham: Springer, September 2018, pp. 597–628.

- P. Chandrasekhar, "CNT Applications in Microelectronics, "Nanoelectronics," and "Nanobioelectronics"," in *Conducting Polymers, Fundamentals and Applications*, Cham: Springer, March 2018, pp. 65–72.

- M. F. L. De Volder, S. H. Tawfick, R. H. Baughman, and A. J. Hart, "Carbon nanotubes: present and future commercial applications," *Science*, Vol. 339, no. 535, pp. 535–539, 2013. DOI:10.1126/science.1222453

- Q. Cao, and J. A. Rogers, "Ultrathin films of single-walled carbon nanotubes for electronics and sensors: a review of fundamental and applied aspects," *Adv. Mater.*, Vol. 21, pp. 29–53, 2009. DOI:10.1002/adma.200801995

- H. Hashempour, and F. Lombardi, "Circuit-Level modeling and detection of metallic carbon nanotube defects in carbon nanotube FETs," in *Proceedings of the IEEE Design*, *Automation & Test in Europe Conference* & Exhibition, Nice, France, Apr. 16–20, 2007, pp. 1–6.

- S. Lin, Y.-B. Kim, F. Lombardi, and Y. J. Lee, "A new SRAM cell design using CNTFETs," in Proceedings of the IEEE International SoC Design Conference, Busan, South Korea, Nov 24–25, 2008, pp. I:168–I:171.

- P. Avouris, J. Appenzeller, R. Martel, and S. J. Wind, "Carbon nanotube electronics," *Proc. of the IEEE*, Vol. 91, no. 11, pp. 1772–1784, 2003. DOI:10.1109/JPROC.2003. 818338

- 13. S. Abdolahzadegan, P. Keshavarzian, and K. Navi, "MVL current mode circuit design through carbon nanotube technology," *Eur. J. Sci. Res.*, Vol. 42, no. 1, pp. 152–63, 2010.

- S. Issam, A. Khater, A. Bellaouar, and M. I. Elmasry, "Circuit techniques for CMOS low power high performance multipliers," *IEEE J Solid-State Circuit*, Vol. 31, pp. 1535–1544, 1996. DOI:10.1109/4.540066

- K. Navi, A. Momeni, F. Sharifi, and P. Keshavarzian, "Two novel ultra-high speed carbon nanotube full-adder cells," *IEICE Electron.*, 1395–1401, 2009. DOI:10.1587/elex.6. 1395

- R. Zimmermann, and W. Fichtner, "Low-power logic styles: CMOS versus pass transistor logic," *IEEE J. Solid-State Circuits*, 1079–1090, 1997. DOI:10.1109/4.597298

- R. F. Mirzaee, M. H. Moaiyeri, and K. Navi, "High speed NP-CMOS and multi-output dynamic full adder cells," *Int. J. Electr. Comput. Sys. Eng.*, Vol. 4, no. 4, pp. 304–10, Mar. 2010.

- 18. C. H. Chang, J. Gu, and M. Zhang, "A review of 0.18  $\mu$ m full adder performances for tree structured arithmetic

circuits," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, 686–695, 2005. DOI:10.1109/TVLSI.2005.848806

- K. Navi, M. Rashtian, O. Hashemipour, A. Khatir, and P. Keshavarzian, "High speed capacitor-inverter based carbon nanotube full adder," *Nanoscale Res. Lett.*, 859–862, 2010. DOI:10.1007/s11671-010-9575-4

- K. Navi, R. S. Rad, M. H. Moaiyeri, and A. Momeni, "A low-voltage and energy efficient full adder cell based on carbon nanotube technology," *Nano. Micro. Lett.*, 114–120, 2010. DOI:10.1007/BF03353628

- A. Khatir, A. Shaghayegh, and M. Iman, "High speed multiple valued logic Full Adder using Carbon nano Field Effect transistor," *Int. J. VLSI Des. Commun. Syst.*, Vol. 2, pp. 1–9, 2011. DOI:10.5121/vlsic.2011.2101

- M. Bagherizadeh1, and M. Eshghi, "Two novel low-power and high-speed dynamic carbon nanotube Full-Adder cells," *Nanoscale Res. Lett.*, Vol. 6, pp. 519–525, 2011. DOI:10.1186/1556-276X-6-519

- R. Uma, and P. Dhavachelvan, "Modified gate diffusion input technique: A new technique for enhancing performance in Full Adder circuits," in *Proceedings of the* 2nd International Conference on Communication, Computing & Security, Rourkela, Odisha, India, Oct. 6–8, 2012, pp. 74–81.

- T. F. Canan, H. Xin, and A. Louri, "10 and 8 T Full adders based on ambipolar XOR gates with SB-FinFETs," in *Proceedings of the 25th IEEE International Conference on Electronics, Circuits and Systems,*, December 9–12, Bordeaux, France, 2018, pp. 577–580.

- S. Hatefinasab, "CNTFET-based design of a high-efficient Full Adder using XOR logic," *J. Nano. Electron Phys.*, Vol. 8, no. 4(2), pp. 04061:1–6, 2016. DOI:10.21272/jnep.8(4(2)). 04061.

- F. Jafarzadehpour, and P. Keshavarzian, "Low-power consumption ternary full adder based on CNTFET," *IET Circuits Devices Syst.*, Vol. 10, no. 5, pp. 365–374, Sep. 2016. DOI:10.1049/iet-cds.2015.0264

- 27. K. C. Sankisa, R. Sahoo, and S. K. Sahoo, "CNTFET Based Quaternary Full adder," in *Fourth International*

Conference on Devices, Circuits and Systems (ICDCS'18), 2018, pp. 181–185.

- B. Srinivasu, and K. Sridharan, "Carbon nanotube FETbased low-delay and low-power multi-digit adder designs," *IET Circuits Devices Syst.*, Vol. 11, no. 4, pp. 352–64, Sep. 2017.

- S. K. Sahoo, G. Akhilesh, and R. Sahoo, "Design of an high performance carry generation circuit for ternary Full Adder using CNTFET," *IEEE Int. Symp. Nanoelectronic Inf. Syst.*, 46–49, 2017. DOI: 10.1109/iNIS.2017.19.

- 30. A. Sadeghi1, N. Shiri1, and M. Rafiee, "High-efficient, ultra-low-power and high-speed 4:2 compressor with a New Full Adder cell for bioelectronics applications," *Circuits Syst. Signal Process.*, Vol. 39, pp. 6247–6275, June 2020. DOI:10.1007/s00034-020-01459-x

- H. T. Tari, A. D. Zarandi, and M. R. Reshadinezhad, "Design of a high performance CNTFET-based full adder cell applicable in:carry ripple, carry select and carry skip adders," *Microelectron. Eng.*, Vol. 215, pp. 110980, 2019. DOI:10.1016/j.mee.2019.110980

- A. Torkzadeh Mahani, and P. Keshavarzian, "A novel energy-efficient and high speed full adder using CNTFET," *Microelectron. J*, Vol. 61, pp. 79–88, 2017. DOI:10.1016/j. mejo.2017.01.009

- S. Hatefinasab, "Design a low power CNTFET-Based Full Adder using majority not function," *Electron J. Biol.*, Vol. 12, no. 1, pp. 12–17, 2016.

- M. H. Moaiyeri, R. Faghih Mirzaee, K. Navi, and A. Momeni, "Design and analysis of a high-performance CNFET-based full adder," *Int. J. Electron.*, Vol. 99, pp. 113–130, 2012. DOI:10.1080/00207217.2011.623269

- A. B. Rahin, and V. B. Rahin, "FinFET-based Full Adder using SDTSPC logic with high performance," *Int. J. Mechatron. Electr, Comput, Technol, (IJMEC)*, Vol. 10, no. 38, pp. 4773–4778, Oct. 2020.

- M. P. Kumar, M. Dharmendra, R. P. Sai, M. D. S. Shrity, and P. Vamsi, "An efficient full adder using FinFET technology," *Int, J, Manage, Technol, Eng.*, Vol. IX, no. Issue III, pp. 4754–4761, Mar. 2019.

### **AUTHORS**

**Priyanka Tyagi** obtained her MTech degree from MDU, Rohtak in 2011 in VLSI Design. She has taught in various reputed institutions such as Manav Rachana University, Faridabad, Priyadarshini College of Computer Sciences, Gr Noida and ABESIT College of Engineering, Ghaziabad. Her research

interest is in low power VLSI Circuits and nanoelectronics.

### Corresponding author. Email: prnktyagi7@gmail.com

Sanjay Singh obtained PhD from Uttarakhand Technical University, Dehradun in 2014 in low power VLSI design. He has taught in various reputed institutions. Currently, he is working in ABES Engineering College, Ghaziabad. He is working also as Editor in *IJAEST* and *IJAEEE Journal* and published various books based on microprocessor and electronics engineering. He has over 15 publications in international and national journals and conferences.

Email: sanjaysinghraj4@gmail.com

**Piyush Dua** obtained his PhD degree from Indian Institute of Technology, Roorkee, India in 2005. After finishing his doctorate, he served in various institutions. Presently, he is working at the University of Technology and Applied Sciences – Suhar, Oman. He has a teaching experience of about 12 years. He has worked as

a post-doctoral scientist at Pohang University of Science and Technology (POSTECH), and has been awarded two projects as principal investigator. He has published 20+ papers in refereed journals of International repute journals including *Journal* of *Biomedical Nanotechnology* and many others.

Email: dua.piyush@gmail.com, piyushd.soh@cas.edu.om